1.7.

Программируемые логические устройства

Существует

множество ИС, у которых выполняемая ими логическая функция может быть

«запрограммирована» уже после их изготовления. В большинстве случаев такие ИС бывают

созданы на основе технологии, допускающей перепрограммирование выполняемой

схемой функции, а это означает, что при обнаружении вами ошибки в

разрабатываемом проекте можно устранить ее без физической замены ИС и без

изменения схемы соединений. В этой книге мы часто будем ссылаться на

предоставляемые возможности с точки зрения проектирования цифровых устройств и на

то, как следует воспользоваться этими возможностями.

Исторически

первыми программируемыми логическими устройствами были программируемые логические матрицы (ПЛМ; programmable logic arrays, PLAs). ПЛМ представляли собой двухуровневую

структуру, состоящую из вентилей И и

ИЛИ, с

программируемыми пользователем соединениями. Используя эту структуру, проектировщик

мог приспособить такую ИС к выполнению любой логической функции, не превосходящей

определенного уровня сложности, на основе известной теории логического синтеза

и минимизации логических схем, которая будет представлена в главе 4.

Конструкция

ПЛМ была усовершенствована, а цена на такие ИС снижена с появлением программируемых

логических устройств решетчатой структуры [programmable array logic (PAL) devices]. Сегодня общее название таких ИС -программируемые

логические устройства (ПЛУ; programmable logic devices, PLDs) и в иерархии изготовляемых промышленностью программируемых устройств они являются схемами «средней степени

интеграции». Об архитектуре и технологии ПЛУ будет многое сказано в

параграфах 5.3 и 8.3.

Постоянно растущая емкость интегральных схем предоставляла производителям возможность

разрабатывать крупные ПЛУ для построения более сложных цифровых устройств. Однако по

техническим причинам, которые мы обсудим в параграфе 10.5, основную двухуровневую структуру И-ИЛИ в ПЛУ

нельзя было расширить до больших размеров.

Вместо этого в промышленности, производящей ИС, произошел переход к

архитектуре составных ПЛУ (complex PLDs, CPLDs), допускающей расширение до требуемого объема. Типичная ИС типа CPLD представляет собой совокупность

нескольких ПЛУ со структурой соединений

между ними, размещенной на том же самом кристалле. Помимо самих ПЛУ, структура соединений в микросхеме также является

программируемой, чем обеспечиваются богатые возможности при

проектировании. ИС типа CPLD можно расширять до больших

размеров путем увеличения числа отдельных ПЛУ и за счет развития

структуры соединений между ними, размещаемой на кристалле.

Примерно в то же время, когда

были созданы ИС типа CPLD, другими производителями ИС был предпринят отличающийся от идеи CPLD подход к проблеме увеличения объема программируемых логических схем. По сравнению с ИС

типа CPLD решетки

вентилей, программируемые в процессе эксплуатации (field-programmable gate arrays, FPGAs) содержат много большее число меньших по размерам отдельных логических блоков и имеют развитую распределенную

структуру внутренних соединений, которая занимает почти весь кристалл.

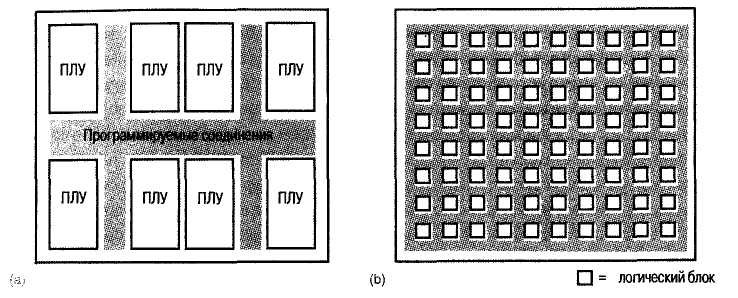

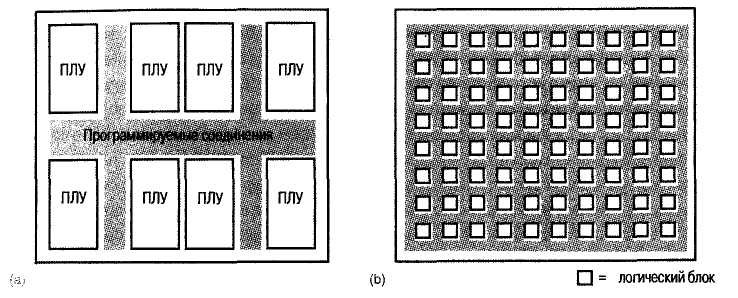

Рис. 1.6 демонстрирует различие между этими двумя

конструкциями микросхем.

Рис. 1.6. Два

подхода к увеличению объема программируемых логических устройств: а) микросхема типа CPLD; (b) микросхема

типа FPGA

Сторонники

того и другого подходов обычно приводят доводы «религиозного» характера

относительно того, какой из принципов лучше, но самый крупный производитель больших программируемых

логических устройств фирма Xilinx, Inc., считает, что у каждого из этих подходов

есть свое место, и производит ИС обоих

типов. Более важным, нежели архитектура микросхем, является то обстоятельство, что оба подхода поддерживают такой

стиль проектирования, который обеспечивает

продвижение изделия от первоначальной идеи до опытного образца и серийного производства за очень короткое

время.

Существенным с точки зрения быстрого появления на рынке изделий на основе ПЛУ всех типов является использование на

стадии проектирования языков описания схем. Такие языки как ABEL и VHDL и сопровождающие их программные средства

позволяют реализовать проект, осуществить синтез и произвести загрузку в ПЛУ и

микросхему типа CPLD

или FPGA буквально за

считанные минуты. Вся мощь структурированных

иерархических языков высокого уровня типа VHDL особенно ярко проявляется в том, что

с их помощью можно создавать конструкции из

сотен тысяч или миллионов вентилей, предоставляемых самыми большими

кристаллами типа CPLD и

FPGA.

![]() 500 Схем для радиолюбителей - Часть 4 - Источники питания

500 Схем для радиолюбителей - Часть 4 - Источники питания![]() Проектирование цифровых устройств Том 1 Джон Ф Уэйкерли

Проектирование цифровых устройств Том 1 Джон Ф Уэйкерли![]() Самоучитель по устранению сбоев и неполадок домашнего ПК

Самоучитель по устранению сбоев и неполадок домашнего ПК![]() Устройства магнитного хранения данных

Устройства магнитного хранения данных![]() Номенклатура и аналоги отечественных микросхем

Номенклатура и аналоги отечественных микросхем